|

|

라디오 전자 및 전기 공학의 백과사전 전계 효과 트랜지스터의 단계 계산. 무선 전자 및 전기 공학 백과사전

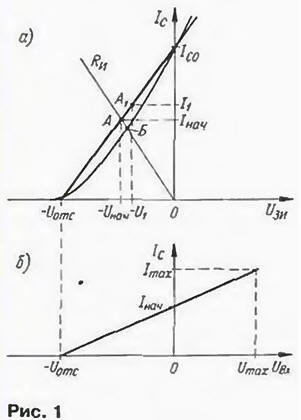

무선 전자 및 전기 공학 백과사전 / 라디오 아마추어 디자이너 이 기사의 저자가 제안한 특성의 선형 근사치를 사용하면 전계 효과 트랜지스터에서 다른 단계의 단계를 계산하는 것이 훨씬 쉬울 것입니다. 컷오프 전압과 특정 트랜지스터 인스턴스의 초기 드레인 전류가 알려진 경우 이러한 단계 계산은 실무와 잘 일치합니다. 거의 모든 문학 출처는 작은 교류 신호 모드에서만 전계 효과 트랜지스터로 증폭 단계의 계산을 설명하는 것으로 알려져 있습니다. 트랜지스터의 초기 모드 선택에 대한 권장 사항조차 찾기가 쉽지 않습니다. 한편, 대부분의 실제 사례에서는 직류에 대한 단계를 계산하는 것이 더 필요합니다. 기사에서 제안된 기술을 사용하면 실제로 가장 일반적인 노드(DC 증폭기, 전류 안정기 등)의 단계를 계산할 수 있습니다. 주파수 신호는 직류에 대한 단계의 일반적인 계산입니다. 명확성을 위해 통합 채널이 있는 n-채널 트랜지스터를 고려하는 것으로 제한합니다. p-채널의 경우 전압의 극성만 변경하면 됩니다. 트랜지스터의 과도 특성 lc=f(Uzi)는 XNUMX차 함수로 근사하는 것으로 인정된다. 이것은 단일 채널 트랜지스터의 경우 대체로 사실이지만 오랫동안 생산이 중단되었습니다. 현재 저전력 전계 효과 트랜지스터조차도 병렬로 연결된 여러 채널 셀의 어셈블리이며 강력한 트랜지스터는 최대 수백, 때로는 수천을 포함합니다. 이러한 요인과 기타 요인으로 인해 이러한 트랜지스터의 실제 과도 응답은 선형 함수와 XNUMX차 함수 사이에 있습니다. XNUMX차 함수에 의한 실제 특성의 근사는 단계 계산의 복잡성으로 이어질 수 있으며, 이는 해당 정확도 증가로 정당화되지 않습니다. 선형 근사를 사용하여 단계를 계산하는 것이 더 편리합니다. 트랜지스터의 과도 응답에는 Uzi = 0에서 결정되는 트랜지스터의 초기 드레인 전류 Ico라는 두 가지 특징적인 점이 있습니다. 소위 컷오프 전압 Uotc (그림 1a). 그리고 첫 번째 질문으로 모든 것이 명확하다면 두 번째 질문에서는 더 어렵습니다.

사실은 과도 특성이 Uzi 축에 점근적으로 경향이 있기 때문에 드레인 전류가 0이 되는 전압(즉, 실제 차단 전압)을 지정하는 것이 불가능합니다. 따라서 드레인 전류가 10μA가 되는 전압, 즉 측정하기 쉬운 값인 조건값 U를 채택했습니다. 그러나 특성이 선형 근사에서 가장 큰 오류 구성 요소를 제공하는 특히 날카로운 굽힘을 갖는 것은 바로 이 지점 근처입니다. 예를 들어 기울기의 미분 값을 줄이는 기준이나 드레인 전류의 특정 값에 따라 굴곡 섹션의 시작 부분에서 두 번째 지점을 결정하는 것이 더 정확할 것입니다. 불행히도 최신 전계 효과 트랜지스터의 과도 특성에 대한 신뢰할 수 있는 통계가 없기 때문에 이 문제를 명확하게 해결할 수 없습니다. 따라서 lco와 Uotc라는 두 개의 기준점에 대한 선형 근사를 받아들여야 합니다. 대부분의 경우 수반되는 오류는 15%를 초과하지 않으며 이는 연습하기에 충분합니다. 무화과. 도 1에서 굵은 직선은 트랜지스터의 실제 특성의 선형 근사를 나타낸다. 무화과. 도 2는 예로서 소스 팔로워 회로를 도시한다. Vin = 0일 때(리피터의 입력을 공통 와이어에 닫는 경우) 작동 지점 A는 과도 특성과 로드 라인 R의 교차점에 있습니다(그림 1). 실제 작동 지점은 실제 과도 응답과 로드 라인의 교차점입니다. 이것은 지점 B입니다. 그림은 선형 근사로 인한 오류의 특성을 보여줍니다.

현재 Istart에 대한 작동 지점 A의 초기 위치는 다음 식을 결정합니다. Istart = Ico / (S·Ri+1). 전압으로 환산하면 Unach Ri = lco Ri Rn/(S Ri+1)로 표현할 수 있다. 여기서 S \u2d lco / Uotc는 특성의 평균 기울기이고 Ri는 저항 Ri의 저항입니다 (그림 XNUMX). 게이트가 공통선에 연결되면 리피터는 전류 안정화 XNUMX단자 네트워크(전류 안정화 장치)가 됩니다. 첫 번째 공식에 따르면 안정화 전류를 계산할 수 있습니다. 장치가 전류 안정화 모드로 들어가는 최소 전압은 입니다. 트랜지스터 채널 UCi의 전압 강하는 출력 특성 계열에 의해 또는 실험적으로 결정됩니다. Ri = 0이면 안정화 전류가 최대이고 Iso와 같으면 출력 저항이 최소이며 트랜지스터의 출력 저항과 거의 같습니다. 소스 팔로워의 입력에 일정한(예: 양의) 전압 Uin을 공급하면 작동 지점이 위치 A로 이동하고 새 전류 좌표 I는 식 Ri+1에 해당합니다. 트랜지스터 폐쇄 전압의 값은 It=0에서 결정되며 Uotc와 같습니다. 전압 측면에서 동작점의 새로운 위치는 Ut=lt Ri=Ri(lco+ Uin.S)/(S Ri+1) 관계식으로 표현할 수 있습니다. 양수 값 영역의 입력 전압 한계는 일반적으로 다음 공식으로 설명됩니다. Uin = [Imax(S·Ri+1)-lco]/S, 여기서 Imax는 트랜지스터의 최대 전류입니다. 최대 전류 Imax. 여러 요인에 의해 제한됩니다. 그래서. p-n 접합 형태의 게이트가 있는 트랜지스터의 경우 Ic0을 초과해서는 안 됩니다. 그렇지 않으면 게이트가 순방향 바이어스 모드로 전환되고 트랜지스터의 입력 저항이 급격히 감소합니다. 이를 염두에 두고 마지막 공식은 Uin = lCo·Ri로 단순화됩니다. 네거티브 전압 측의 작동 간격 경계는 트랜지스터의 초기 작동 모드에 의존하지 않으며 항상 Uotc에서 시작합니다. 따라서 동작 간격을 늘리기 위해서는 Uotc 값이 큰 트랜지스터를 선택해야 합니다. 절연 게이트 트랜지스터의 경우 값은 장치에 허용되는 전류 제한 또는 허용 가능한 전력 손실에 의해서만 제한됩니다. 어쨌든 1max. Upit/Ri를 초과할 수 없습니다. 특정 단계에 대한 단계를 계산할 때 I의 값은 위에서 설명한 각 요소에 의해 결정되고 가장 작은 것이 선택되며 이것이 공식으로 대체됩니다. Ut에 대한 식을 변환하면 Ut = Ico Ri/(S Ri+1 )+Uin S Ri/ (S Ri+1)을 얻습니다. 이 공식은 스트리밍 리피터의 특성 Uout = f(Uin,)이 선형임을 명확하게 보여줍니다. 소스 팔로워의 변환 경사도 Kns는 다음과 같습니다. Кns = ΔImax/ ΔUin = S/(S·Ri + 1). 따라서 전압 전달 계수 Knu = Knl·Ri = S·Ri/(S·Ri+1)이 된다. 무화과. 1b는 소스 팔로워의 특성 Ic = f(Uin)을 보여준다. 전달 특성 Uout = f(Uin)은 유사한 형태를 가집니다. Uout \uXNUMXd Ic·Ki 이후. 무화과. 도 3은 저항 R 및 자동 바이어스를 갖는 공통 소스 회로에 따라 트랜지스터가 조립되는 전형적인 증폭 단계의 다이어그램을 보여준다.

트랜지스터의 초기 모드는 이 저항의 저항에 의해 결정됩니다. 트랜지스터의 전류 모드를 설정할 때(입력 신호가 없는 경우) 저항의 저항은 다음 공식으로 결정할 수 있습니다. Rand \uXNUMXd (Iso "Inach) / Inach S. 일반적으로 동작점은 특성의 중간, 즉 Istart = Ico / 2 및 Ustart = Uotc / 2에서 선택되며 이 공식은 R 및 = I / S = Uotc / Ico로 단순화됩니다. 특성에 대한 동작점의 초기 위치가 비대칭이어야 하는 경우(예: 비대칭 입력 신호의 경우), 주어진 Uinit 값에서 저항 Rand의 저항, 초기 오프셋은 다음 공식에 의해 결정됩니다. Ri = Uinit / (lco-Uinit S). 트랜지스터 드레인의 전압은 Uc \uXNUMXd Upit - Inach ·Rc와 같습니다. 대칭 신호의 경우 왜곡이 없을 때 출력 전압의 최대 범위를 제공하는 저항 Rc의 저항은 Rc \u2d (Upit-Unach) / 0.5I 공식으로 구합니다. 트랜지스터의 전달 특성 중간에서 동작점을 선택하면 Rc = (Upit - XNUMXUotc)lco. 저항 R은 네거티브 OS의 요소입니다. 감소 단계. 교류 전압에서 OS의 동작을 제거하기 위해 일반적으로 그림 3에 표시된 차단 커패시터 Cbl을 포함합니다. 점선 XNUMX개. 이 커패시터를 사용하면 입력 신호의 음의 반파 진폭이 트랜지스터의 차단 전압과 같은 값을 초과해서는 안됩니다. 다른 방법으로 교류 전압에 대한 OS의 작용을 제거하는 것도 가능합니다. 저항 대신 트랜지스터의 소스 회로에 전압이 흐르는 전류에 거의 의존하지 않는 요소, 예를 들어 직접 다이오드, 스태비스터 등 그러나 이러한 회로 설계 솔루션은 이 요소의 전압이 Unach와 같은 경우에만 가능합니다. 요소의 전압이 다소 낮 으면 작은 저항의 추가 저항이 직렬로 연결됩니다. 공통 소스 회로에 따라 조립된 스테이지의 전달 계수 Knu는 잘 알려진 식 Knu=S·Rc로 결정됩니다. 소스 회로에 저항이 있으면 Knu는 감소합니다: Knu=S·Rc/ (S·Ri+1)=lco·Rc/(lco·Ri+Uotc). 트랜지스터 VT1(출력 1)의 드레인 신호는 입력과 역상이고 소스(출력 2)의 신호는 동위상이므로 이 스테이지를 위상 스플리터로 사용할 수 있습니다. 일반적으로 위상 스플리터는 두 출력의 신호 진폭 값이 동일해야 합니다. Uout1 = Uout2 또는 lc·Rc=lи·Rи. lc=XNUMX이고 진폭이 같은 조건은 다음과 같습니다. Rc = Rand. 이 경우 두 출력의 전송 계수 값도 동일합니다. 전달 계수, 저항 Rc 및 Rand의 저항. 위에 제시된 공식을 사용하여 기타 필요한 매개변수를 계산할 수 있습니다. 예를 들어, 그림 3의 계획에 따른 단계가 수행되는 조건을 고려하십시오. 1은 출력 1을 Knu = XNUMX인 선형 인버터로 켭니다. 마지막 공식에서 Knu를 XNUMX로 동일시하면 다음을 얻습니다. Rc-Ri \u1d XNUMX / S \uXNUMXd Uotc / Ico. 이러한 단계는 바이폴라 트랜지스터의 유사한 단계와 유사하게 드레인 팔로워라고 부를 수 있습니다. 저자: A. Mezhlumyan, 모스크바

광신호를 제어하고 조작하는 새로운 방법

05.05.2024 프리미엄 세네카 키보드

05.05.2024 세계 최고 높이 천문대 개관

04.05.2024

▪ 초점에 태양 ▪ 가장 큰 물고기 ▪ 음향 부상자

▪ 기사 사람의 낙관주의와 비관주의를 주로 결정하는 것은 무엇입니까? 자세한 답변 ▪ 기사 Z8 마이크로컨트롤러의 전원 조정기. 무선 전자 및 전기 공학 백과사전 ▪ 기사 갈바닉 절연이 있는 네트워크 어댑터, 220/9볼트. 무선 전자 및 전기 공학 백과사전

홈페이지 | 도서관 | 조항 | 사이트 맵 | 사이트 리뷰 www.diagram.com.ua |

Arabic

Arabic Bengali

Bengali Chinese

Chinese English

English French

French German

German Hebrew

Hebrew Hindi

Hindi Italian

Italian Japanese

Japanese Korean

Korean Malay

Malay Polish

Polish Portuguese

Portuguese Spanish

Spanish Turkish

Turkish Ukrainian

Ukrainian Vietnamese

Vietnamese

이 기사에 대한 의견을 남겨주세요:

이 기사에 대한 의견을 남겨주세요: